|

1 G5 y- O# J) m! q

1. USB2.0USB2.0是应用时间最长久的USB总线虽然USB3.x已发布很久,USB4的2.0版都发布了,但USB2.0却还在广泛应用中那么,对于用了这么久的USB2.0,你知道哪些基础知识呢?下面,我来为大家做个简要介绍:。

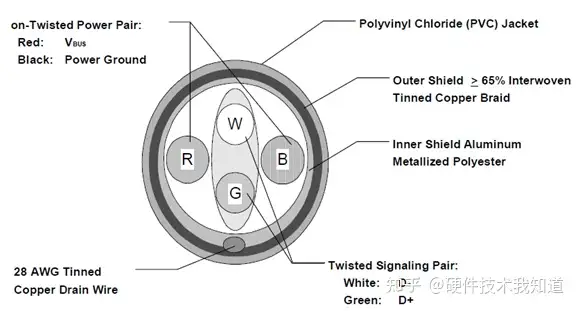

5 {7 D! ~+ a! N) n: u& L% x# S 1.1USB2.0使用差分信号传输数据USB2.0使用一对差分信号传输数据,并可以为USB设备提供电源差分信号名称一般标示为“D+”和“D-”建议“D+”信号使用绿色线,“D-”信号使用白色线建议电源正极使用红色线,回路地使用黑色线。

8 G& J; x" E% P o9 N 所有线的外层,必须先包一层屏蔽层再包外皮如下图所示   6 l# Q9 a6 O' C) m3 `, d

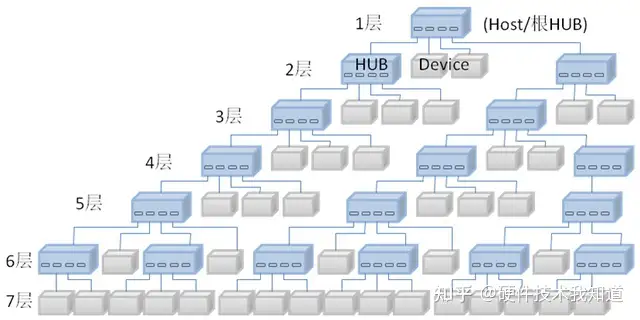

6 l# Q9 a6 O' C) m3 `, d 1.2层次星型拓朴结构由于USB采用差分信号传输数据,只能采用点对点的连接方式,导致USB系统只能使用星型拓扑结构。如下图所示。  ) ]$ f; t# E, k; F# q ) ]$ f; t# E, k; F# q

在一个USB2.0总线系统中,有且只能有一个主机(Host),最多可以支持126个设备(含Host共127),最多可以连接7个层级(包含Host/根层)一条USB电缆最长可以做到5m,因此,一个链路最长的传输距离大约为30m(5m×6)。 # m/ N' Z: E( `7 B# c7 Y

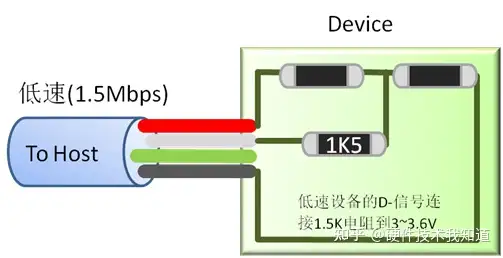

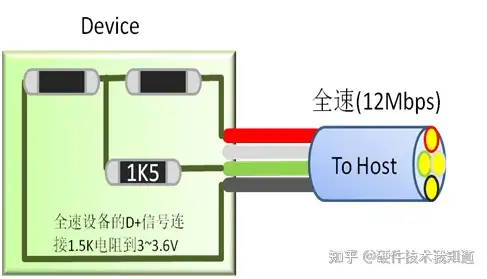

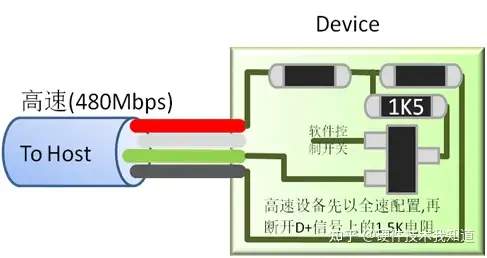

1.3 USB2.0支持三种传输速率USB2.0可以支持三种传输速率:低速USB设备传输速率为1.5Mbps,全速USB设备传输速率为12Mbps,高速USB设备传输速率为480Mbps在硬件电路方面,低速USB设备内部的“D-”信号应该通过1.5K的电阻上拉到3~3.6V;全速USB设备内部的“D+”信号应该通过1.5K的电阻上拉到3~3.6V;高速USB设备内部的“D+”信号先是通过1.5K的电阻上拉到3~3.6V,然后断开上拉电阻由软件配置成高速设备。 , P, \5 c% Q0 S" `9 \

在USB上游设备中,“D+”和“D-”信号应该通过15K电阻下拉到地平常,上游USB接口被15K电阻下拉到地,为低电平当USB设备插入上游USB接口时:如果“D-”信号被拉成高电平,则USB系统知道接入的是低速USB设备。 4 e, E$ L4 T7 V

将该端口配置成低速模式如果是“D+”信号被上拉变成高电平,则USB系统知道接入的是全速USB设备将该端口配置成全速模式高速USB设备则是先配置成全速模式,再配置成高速模式如下图所示    ) \% \, L L' o8 | o {( V9 Y

) \% \, L L' o8 | o {( V9 Y 1.4 USB枚举过程和六种状态USB枚举过程大致如下:a) USB设备插入USB系统中的某USB上游端口b)该上游USB端口向USB设备提供电源Vbus(连接状态)c)USB设备驱动“D+”或“D-”信号为高电平(。

6 r! E+ W8 |$ ?6 R @/ ^# B* _' F 上电状态)d)上游端口向USB设备请求设备描述符(缺省状态)e)USB设备向上游端口报告设备的部分信息(缺省状态)f)上游端口为USB设备设置地址(地址状态)g)USB设备进入新的地址(地址状态)j)上游端口向USB设备请求配置描述符( & M4 B/ A) D9 A9 }' j9 S2 E

配置状态)i)USB设备向上游端口报告设备的完整信息(配置状态)j)上游端口配置USB驱动或USB接口等等(配置状态)k)下游USB端口响应配置(配置状态)i)如果USB设备3~10ms不活动,收进入休眠状态。

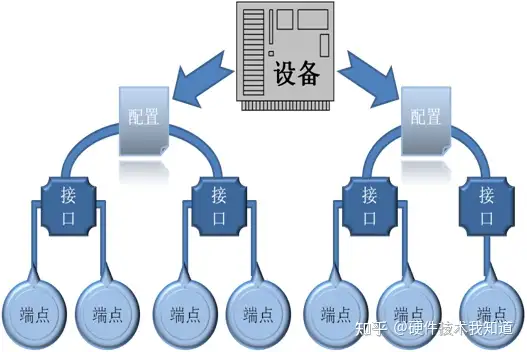

. ~6 Q) C$ l. o9 h: N1 t/ v7 v; y: ` 1.5 USB设备架构一个USB设备,可以拥有多个配置。一个USB配置,可以拥有多个接口;一个USB接口,可以拥有多个端口。请参考下面的示意图。  % O8 X" d7 t! `) Y m

% O8 X" d7 t! `) Y m 1.6 USB2.0常用连接器1.6.1 A型插座。一般安装在上游设备上。比如计算机主板,PCI界面的USB卡等等。  . v; S4 Y y) ] ^# Z . v; S4 Y y) ] ^# Z

1.6.2 B型插座。一般安装在下游设备上。比如打印机,扫描仪等等。  ) }2 O$ d9 a8 A$ u

) }2 O$ d9 a8 A$ u 1.6.3 Mini-B型插座。一般安装在小型USB设备上。比如MP3、MP4、USB小音箱等。  # m6 | S/ J: t5 ` # m6 | S/ J: t5 `

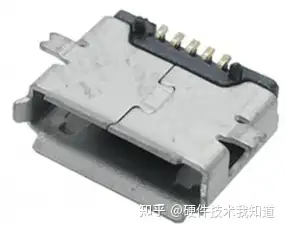

1.6.4 Micro-B、Micro-AB。一般安装在又小又薄的USB设备上。   5 o2 }* m) A4 I2 G: _ 5 o2 }* m) A4 I2 G: _

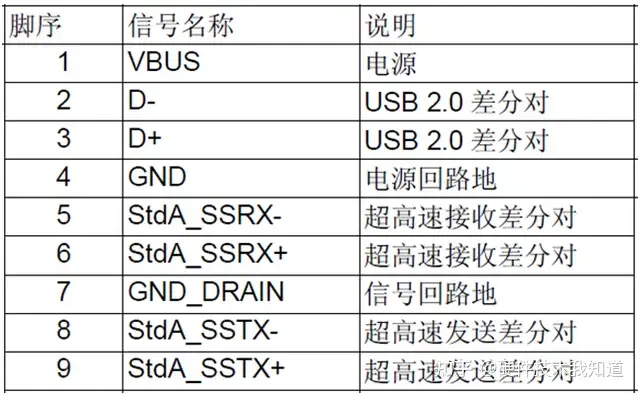

2. USB3.x这里说的USB3.x是指USB3.0、USB3.1、USB3.22.1 USB3.x总线信号在USB3.x总线中,保留完整的USB2.0信号,并可以独立使用另外新增两对高速差分对,分别用于发送和接收。

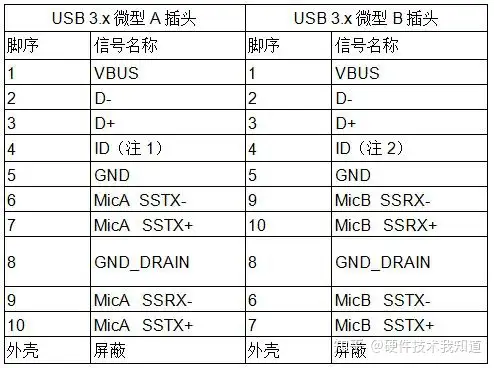

, a7 Q& K8 a6 S 可同时双向传输信号名称如下表:  1 Z9 k. {& n( U% ]& w* L0 |4 @

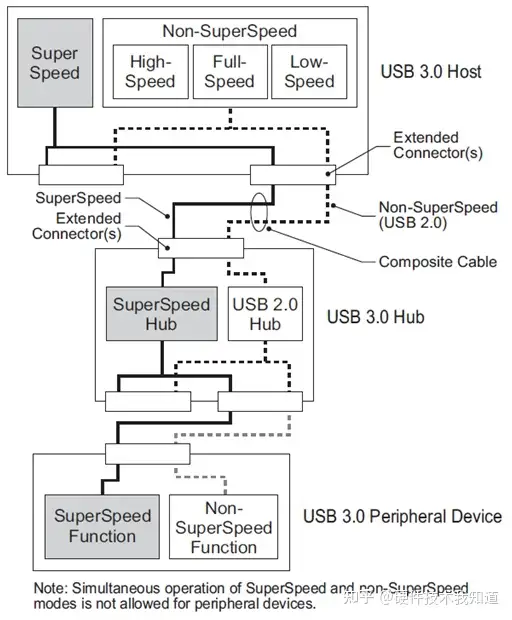

1 Z9 k. {& n( U% ]& w* L0 |4 @ 2.2 USB3.x采用双总线系统结构USB3.x本质上是启用了一套新的总线协议,为了向后兼容,保留了原来的USB2.0协议所以,在USB3.x系统中,是USB2.0和USB3.x两个总线同时在运行如下图所示:。  6 L+ p( d2 N8 r" {3 [ 6 L+ p( d2 N8 r" {3 [

2.3 USB3.x传输速率USB3.0的传输速率为5Gbps称为超高速,后来被称为Gen1USB3.1的传输速率为10Gbps称为超高速+,后来被称为Gen2USB3.2利用Type-C双倍信号线的优势,实现了传输速率翻倍,即Gen1*2=10Gbps;Gen2*2=20Gbps;。

7 ]# B2 ?" v2 L& K. c 2.4 USB3.x连接器2.4.1 A型USB3.x插座  9 g' M1 D, d; {/ U2 l! y8 J 9 g' M1 D, d; {/ U2 l! y8 J

2.4.2 B型USB3.x插座  % h1 J$ s) c% S % h1 J$ s) c% S

2.4.3 Micro-B型USB3.x插座  " A4 W; i4 {0 G

" A4 W; i4 {0 G 2.4.4 C型USB插座(Type-C连接器较早就在用,但是是在单独的规范文件中出现)  5 S3 L. m6 a: }

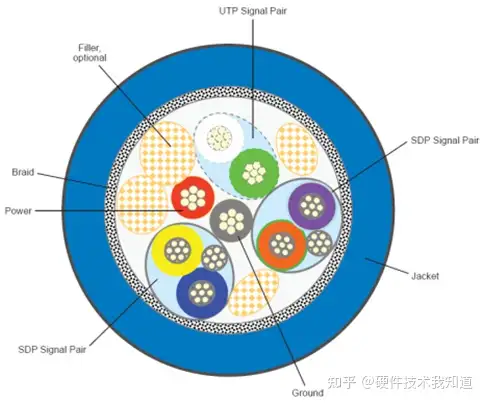

5 S3 L. m6 a: } 2.5 USB3.x电缆基本要求在USB3.x电缆中,除了USB2.0需要用到的非屏蔽双绞线和电源线地线外,还增加了两对屏蔽双绞线,用于发送差分对和接收差分对。如下图所示。  - ~/ h/ }+ m9 Q9 P0 k, f/ o - ~/ h/ }+ m9 Q9 P0 k, f/ o

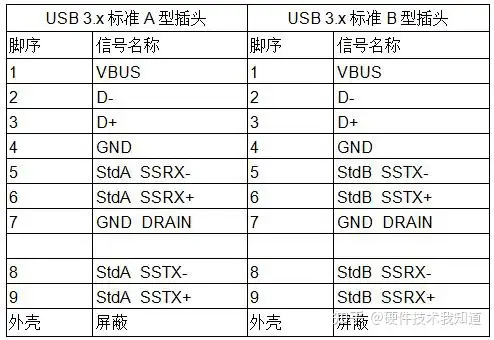

2.6 USB3.x互连电缆由于USB2.0和USB3.x用到的连接器种类繁多,导致USB设备之间的互联电缆也是品种繁多下面简要介绍几款常用电缆的内部连线方法2.6.1 USB 3.x标准A型插头连接到USB 3.x标准B型插头的电缆,其内部连线如下表:。  8 O+ q! p& o/ [2 `

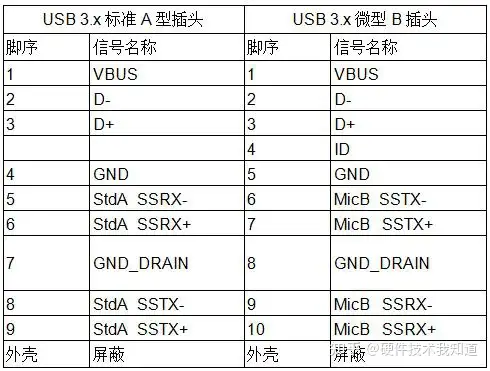

8 O+ q! p& o/ [2 ` 2.6.2 USB 3.x标准A型插头转接到USB 3.x微型B插头的电缆,其内部连线如下表:  7 B m+ n' F- L O1 b/ z1 Q, t

7 B m+ n' F- L O1 b/ z1 Q, t 2.6.3 USB 3.x微型A插头转接到USB 3.x微型B插头的电缆,其内部连线如下表  3 M# n2 f. k' ^- ~: q

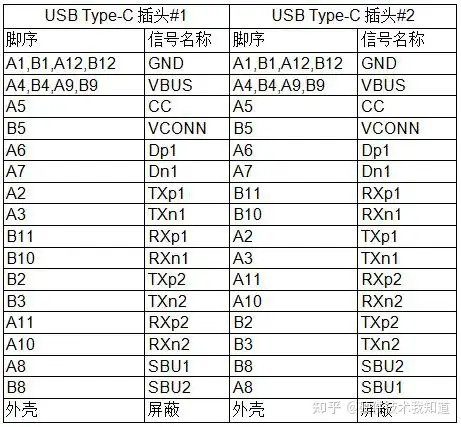

3 M# n2 f. k' ^- ~: q 2.6.4 标准全功能USB Type-C互连电缆,两端都是USB Type-C插头,其电缆内部连线如下表。  3 |. P. \0 k) u% T3 Q

3 |. P. \0 k) u% T3 Q 2.6.5 仅支持USB 2.0的USB Type-C互连电缆,不需要SDP(屏蔽双绞线),其电缆内部连线如下表:  - d' R: H9 M* q8 ]

- d' R: H9 M* q8 ] 2.6.6 USB Type-C插头转接到USB 3.x标准A型插头的互连电缆,其内部连线如下表:  - K. L* n% L) ?! g C0 j @/ P# h - K. L* n% L) ?! g C0 j @/ P# h

2.6.7 USB Type-C插头转接到USB 2.0标准A型插头,其互连电缆内部连线如下表:  a0 B) j1 S( ]5 v0 b8 Q

a0 B) j1 S( ]5 v0 b8 Q 2.6.8 USB Type-C插头转接到USB 3.x标准B型插头的互连电缆,其内部连线如下表。  / {, |' K6 G4 G# g5 r / {, |' K6 G4 G# g5 r

3. USB4USB4结束了USB连接器种类繁多的局面,只使用Type-C连接器USB4 1.0的传输速率是20Gbps,称为Gen3,利用Type-C的双通道,可以实现Gen3*2=40Gbps的传输速率。 - z+ C% |1 {3 ^" q' {

刚刚发布的USB4 2.0的传输速率可达40Gbps,利用Type-C的双通道,可以实现80Gbps的传输速率3.1 USB4使用双总线系统架构USB4仍然使用双总线系统架构和USB3.x一样,是以USB2.0+USB4的形式存在。 7 p" a& ? _3 R' \6 Q; n

如有需要,可以把USB2.0分离出来单独使用如下图所示  ; f9 F8 M: c: m4 G" B

; f9 F8 M: c: m4 G" B 3.2 USB4的隧道USB4引入了隧道的概念,USB3.x的数据流、DP的数据流、PCIe的数据流都可以被打包,在USB4系统中传输。请参阅如下示意图    + d5 D3 P& n3 |) T0 c

+ d5 D3 P& n3 |) T0 c 无论是从逻辑分层还是数据编解码等方面来看,USB4已经越来越像PCIe总线了,如要了解更多细节,可参阅规范文件或《工业计算机硬件技术支持手册》下次如果有时间,且读者需要,我再整理一些USB OTG及USB各种充电协议或其它USB相关知识。 2 y) G" a$ A. v3 ~, F6 F$ [2 P

但如果需要的人不多,就算了需要的可以给我留言推荐文章:什么是IP地址?什么是MAC地址?IP地址和MAC地址有什么不同?什么是PoE?PoE如何供电?PoE供电能力如何?半导体集成电路常见封装汇总如何刷新网卡MAC地址?

5 m( G; y1 @# T, ? Intel网卡MAC地址刷新工具EEUPDATE.EXE使用说明 ) N7 h9 K) I0 E9 ~* q7 T& K

% t& D# v( x/ |

7 i6 i; f) Q8 x/ b+ c7 F" I( W* D0 K

" L. s" S( ^+ B( E+ O

- r: a' }& k6 Y* }2 K |